PCB設(shè)計(jì)中高速信號(hào)的影響

- 發(fā)表時(shí)間:2021-06-16 15:25:06

- 來(lái)源:本站

- 人氣:1157

設(shè)計(jì)人員不斷面臨提高電子產(chǎn)品性能的挑戰(zhàn)。同時(shí),設(shè)計(jì)人員需要考慮高速信號(hào)在 PCB 設(shè)計(jì)中的影響,因?yàn)椴粩嘣黾訒r(shí)鐘頻率和減少上升時(shí)間可能會(huì)導(dǎo)致信號(hào)完整性問(wèn)題。這需要使用更高的頻率,50MHz 到 3GHz 的頻率已經(jīng)變得非常普遍。

設(shè)計(jì)高速 PCB 對(duì)支持實(shí)際應(yīng)用至關(guān)重要。PCB 處理高速信號(hào)時(shí),信號(hào)傳輸問(wèn)題尤為突出。一塊出色的高速板是一種集成各種組件和布線(xiàn)同時(shí)避免信號(hào)完整性問(wèn)題的板。我們?cè)诟哳l板中面臨的三個(gè)主要挑戰(zhàn)是信號(hào)完整性、EMI/EMC和介電損耗。

在這篇博文中,我們將討論在 PCB 設(shè)計(jì)中處理高速信號(hào)時(shí)需要注意的以下因素:

PCB中的高速信號(hào)是什么?

為什么高頻下總是有信號(hào)失真?

我們什么時(shí)候需要注意高速 PCB 設(shè)計(jì)中的信號(hào)完整性?

克服高速 PCB 設(shè)計(jì)中信號(hào)完整性問(wèn)題的技術(shù)

高速 PCB 設(shè)計(jì)人員的快速提示

高速印刷電路板材料

為什么在高速 PCB 設(shè)計(jì)中包含設(shè)計(jì)模擬和檢查很重要?

PCB中的高速信號(hào)是什么?

頻率范圍從 50 MHz 到高達(dá) 3 GHz 的信號(hào)被認(rèn)為是高速信號(hào),例如時(shí)鐘信號(hào)。理想情況下,時(shí)鐘信號(hào)是方波,但實(shí)際上不可能立即將其“低”電平更改為“高”電平(反之亦然)。它具有特定的上升和下降時(shí)間,因此它在時(shí)域中看起來(lái)是梯形。值得注意的是,時(shí)鐘信號(hào)在頻域中的較高頻率諧波的幅度取決于其上升和下降時(shí)間。如果上升時(shí)間長(zhǎng)于諧波的幅度會(huì)變小。

為什么高頻下總是有信號(hào)失真?

在低頻 (>1kHz) 下,信號(hào)保持在數(shù)據(jù)特征限制內(nèi),系統(tǒng)按預(yù)期運(yùn)行。當(dāng)速度增加時(shí),更高的頻率影響開(kāi)始發(fā)揮作用,導(dǎo)致振鈴、串?dāng)_、反射、地彈和阻抗不匹配問(wèn)題。它不僅會(huì)影響系統(tǒng)的數(shù)字特性,還會(huì)影響模擬特性。這些問(wèn)題更容易增加I/O 接口和內(nèi)存接口的數(shù)據(jù)速率。實(shí)際上,這些問(wèn)題可以通過(guò)采用先進(jìn)的PCB 設(shè)計(jì)服務(wù)或遵循嚴(yán)格的布局指南來(lái)避免。信號(hào)路由、端接方案和電源分配技術(shù)可以幫助設(shè)計(jì)人員實(shí)現(xiàn)有效的 PCB。

我們什么時(shí)候需要注意高速 PCB 設(shè)計(jì)中的信號(hào)完整性?

信號(hào)完整性:理想情況下,在 PCB 中,信號(hào)應(yīng)該從源 (Tx) 傳輸?shù)截?fù)載 (Rx) 未受損/未摻雜。但實(shí)際上,它不會(huì)發(fā)生。信號(hào)到達(dá)負(fù)載時(shí)會(huì)有一些損耗(阻抗失配、串?dāng)_、衰減、反射、開(kāi)關(guān)問(wèn)題)。信號(hào)完整性 (SI) 是定義用于測(cè)量高頻區(qū)域中這些信號(hào)失真的術(shù)語(yǔ)。信號(hào)完整性通過(guò)提供實(shí)用的解決方案來(lái)幫助預(yù)測(cè)和理解這些關(guān)鍵問(wèn)題。

高速 PCB 設(shè)計(jì)需要將走線(xiàn)可視化為傳輸線(xiàn)而不是簡(jiǎn)單的電線(xiàn)。識(shí)別設(shè)計(jì)中的最高工作頻率有助于定位應(yīng)視為傳輸線(xiàn)的走線(xiàn)。如果走線(xiàn)超過(guò)該頻率波長(zhǎng)的1/10左右,則可以將它們視為傳輸線(xiàn)。這些傳輸線(xiàn)需要數(shù)字和模擬分析。

PCB 基板:PCB 構(gòu)造過(guò)程中使用的基板材料會(huì)導(dǎo)致信號(hào)完整性問(wèn)題。每個(gè) PCB 基板具有不同的相對(duì)介電常數(shù) (ε r ) 值。它決定了信號(hào)走線(xiàn)必須被視為傳輸線(xiàn)的長(zhǎng)度,當(dāng)然,在這種情況下,設(shè)計(jì)人員需要注意信號(hào)完整性威脅。

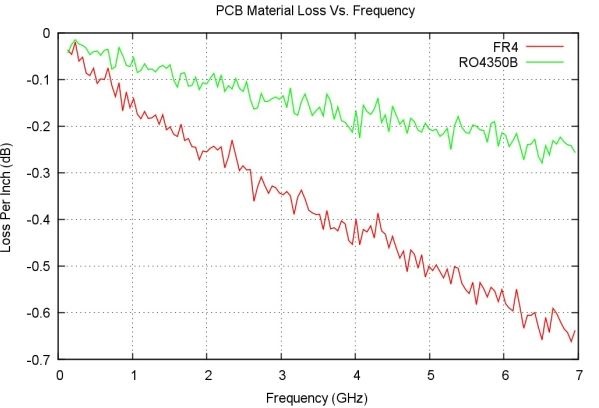

使用 ε r 值,設(shè)計(jì)人員可以評(píng)估信號(hào)流動(dòng)的速度 (V p ) 和傳播延遲( t PD ) 。這些參數(shù)有助于確定應(yīng)將走線(xiàn)視為傳輸線(xiàn)的長(zhǎng)度。下圖描述了插入損耗如何隨信號(hào)頻率增加。插入損耗(每英寸)是針對(duì) FR-4(玻璃環(huán)氧樹(shù)脂)和高頻Rogers RO4350B材料測(cè)量的。更高的插入損耗可能會(huì)導(dǎo)致更大的衰減。單擊此處了解有關(guān)PCB 材料和層壓板的更多信息。

克服高速 PCB 設(shè)計(jì)中信號(hào)完整性問(wèn)題的技術(shù)

設(shè)計(jì)人員可以在高速 PCB 中實(shí)現(xiàn)以下設(shè)計(jì)技術(shù):

1. 高速PCB設(shè)計(jì)中的阻抗匹配

此參數(shù)對(duì)于更快和更長(zhǎng)的跟蹤運(yùn)行很重要。影響阻抗控制的三個(gè)因素是基板材料、走線(xiàn)寬度和走線(xiàn)距離接地/電源層的高度。

在低頻下,PCB 走線(xiàn)由其直流特性定義。它可以被認(rèn)為是一個(gè)理想的電路,沒(méi)有電阻、電容和電感。當(dāng)頻率上升時(shí),與軌道相關(guān)的電感和電容開(kāi)始影響其性能。由于過(guò)孔短截線(xiàn)和走線(xiàn)缺陷導(dǎo)致走線(xiàn)阻抗失配不允許信號(hào)在接收器(負(fù)載)內(nèi)被完全吸收;這就是為什么額外的能量被反射到發(fā)射器(源)的原因。這個(gè)過(guò)程一次又一次地重復(fù),直到所有的能量都被吸收。在高數(shù)據(jù)速率下,它會(huì)導(dǎo)致信號(hào)過(guò)沖、下沖和振鈴,從而產(chǎn)生信號(hào)錯(cuò)誤。為了解決這個(gè)問(wèn)題,這些傳輸線(xiàn)在其下方設(shè)有接地層和終端電阻。

計(jì)算線(xiàn)路的阻抗很重要。(它是綜合線(xiàn)路粗細(xì)、板的介電常數(shù)、線(xiàn)路與地平面的距離來(lái)計(jì)算的。)有時(shí),傳輸線(xiàn)需要穿越不同的層,因此,線(xiàn)路與地平面的距離。地平面發(fā)生變化。在這種情況下,可以通過(guò)改變線(xiàn)路粗細(xì)將線(xiàn)路阻抗保持在相同的值。

注意:對(duì)于高頻、高速設(shè)計(jì),PCB 走線(xiàn)被視為傳輸線(xiàn)。

1.1 高速PCB設(shè)計(jì)中的阻抗控制措施

阻抗失配可以通過(guò)實(shí)施適當(dāng)?shù)亩私臃桨竵?lái)控制。端接方案的選擇取決于應(yīng)用。讓我們討論其中的一些。

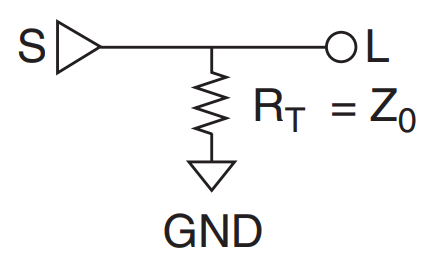

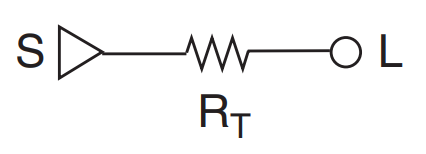

1.1.1 并聯(lián)終端方案:在該方案中,終端電阻(RT)等于線(xiàn)路阻抗。該終端電阻盡可能靠近負(fù)載放置,以實(shí)現(xiàn)最高效率。該終端電阻的電流負(fù)載在高輸出狀態(tài)下最大。

并行端接可在高速 PCB 中提供最高效率。

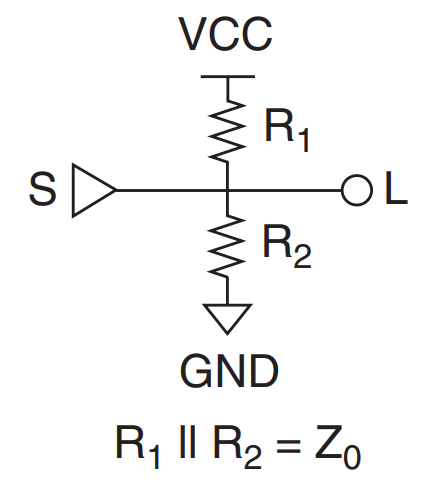

1.1.2 戴維寧終端方案:它是并聯(lián)終端方案的替代方案,其中終端電阻器 (RT) 被分成兩個(gè)獨(dú)立的電阻器,其等于線(xiàn)路阻抗(組合時(shí))。該方案減少了從電源汲取的總電流并增加了從電源汲取的電流,因?yàn)殡娮璺胖迷?VCC 和地之間。

高速 PCB 中的戴維寧終端。

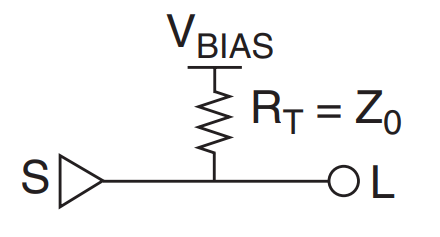

1.1.3 有源并聯(lián)端接:此處,等于線(xiàn)路阻抗(Z0)的端接電阻放置在偏置電壓路徑中。偏置電壓的排列使得輸出驅(qū)動(dòng)器可以從高電平和低電平信號(hào)中提取電流。這種技術(shù)需要一個(gè)單獨(dú)的電壓源,它可以吸收和提供電流以匹配輸出傳輸速率。

高速 PCB 中的有源并行端接。

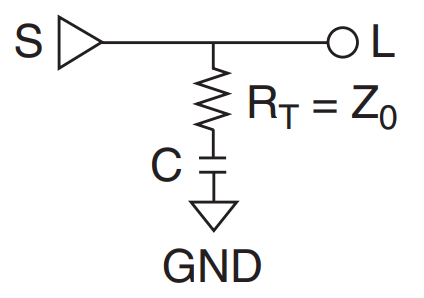

1.1.4 串聯(lián)-RC 并聯(lián)終端:在該方案中,電阻和電容(>100pF)組合作為終端阻抗。此處,終端電阻 (RT) 等于 Z0,電容器阻擋低頻信號(hào)分量并通過(guò)高頻分量。因此,RT 的直流負(fù)載效應(yīng)不會(huì)影響驅(qū)動(dòng)器。

高速 PCB 中的串聯(lián)-RC 并聯(lián)端接。

1.1.5 串聯(lián)端接:匹配信號(hào)源的阻抗,而不是匹配負(fù)載。該方案有助于衰減二次反射。線(xiàn)路阻抗因負(fù)載分布而異。因此,單個(gè)電阻值并不適用于所有條件。這種方法在源端只需要一個(gè)組件,而不是在每個(gè)負(fù)載上需要多個(gè)組件,但通過(guò)增加 RC 時(shí)間常數(shù)來(lái)延遲信號(hào)路徑。

高速 PCB 中的串聯(lián)端接。

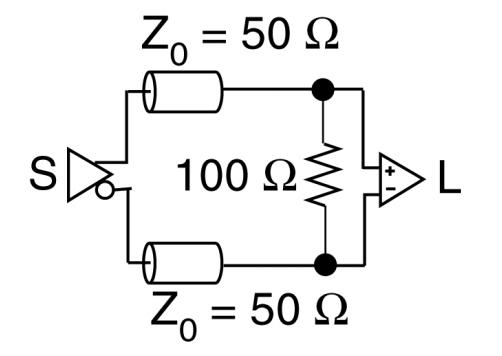

1.1.6 差分對(duì)終端:在接收設(shè)備的信號(hào)之間需要一個(gè)終端電阻。端接電阻必須與差分負(fù)載阻抗匹配(通常為 100Ω)。

高速 PCB 設(shè)計(jì)中的差分對(duì)端接。

2. 高速PCB設(shè)計(jì)中的衰減

高頻傳輸介質(zhì)使接收器難以解釋正確的信息。傳輸介質(zhì)會(huì)導(dǎo)致以下傳輸損耗:

2.1 介質(zhì)吸收:高頻介質(zhì)中的信號(hào)使PCB介質(zhì)材料吸收信號(hào)能量。它會(huì)降低信號(hào)強(qiáng)度。它只能通過(guò)選擇完美的PCB材料來(lái)控制。

2.2 趨膚效應(yīng):高頻信號(hào)也負(fù)責(zé)產(chǎn)生電流值變化的波形。此類(lèi)信號(hào)具有自感值,這會(huì)在高頻下引發(fā)增加的感抗。它負(fù)責(zé)減少 PCB 表面的導(dǎo)電面積,增加電阻,并衰減信號(hào)強(qiáng)度。可以通過(guò)增加軌道寬度來(lái)減少趨膚效應(yīng),但這并不總是可行的。

高速PCB設(shè)計(jì)中的衰減控制

除了仔細(xì)選擇 PCB 絕緣體材料和走線(xiàn)布局外,還可以通過(guò)包括可編程差分輸出電壓、預(yù)加重和接收器均衡來(lái)減少信號(hào)衰減。差分輸出電壓的增加有助于改善接收器的信號(hào)。預(yù)加重是僅通過(guò)增加第一個(gè)傳輸符號(hào)的電平來(lái)增強(qiáng)高頻信號(hào)分量的方式。接收器均衡電路衰減低頻信號(hào)分量以彌補(bǔ)傳輸線(xiàn)損耗。

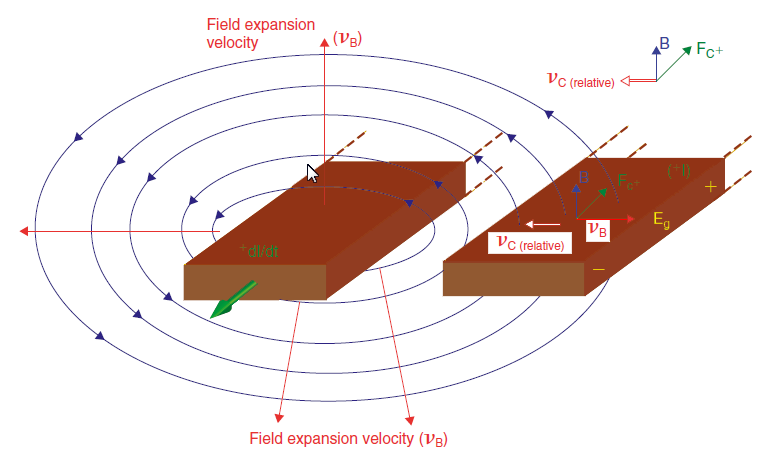

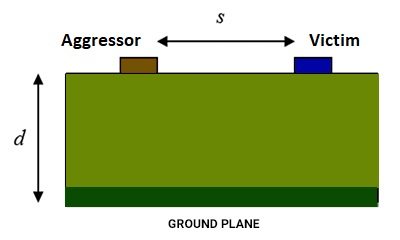

3.高速PCB設(shè)計(jì)中的串?dāng)_

作為電子行業(yè)的愛(ài)好者,我們都知道當(dāng)電流(例如信號(hào))通過(guò)電線(xiàn)時(shí),它會(huì)在其附近產(chǎn)生磁場(chǎng)。如果附近有兩根電線(xiàn),則兩個(gè)磁場(chǎng)可能會(huì)相互作用,導(dǎo)致兩個(gè)信號(hào)之間的能量交叉耦合,稱(chēng)為串?dāng)_。明顯地,電感耦合(由空閑線(xiàn)上源線(xiàn)的磁場(chǎng)感應(yīng)出的電流)和電容耦合(當(dāng)空閑線(xiàn)暴露于與源中電壓變化率成正比的電流量時(shí)的電場(chǎng)耦合線(xiàn))負(fù)責(zé)導(dǎo)致串?dāng)_的能量交叉耦合。

高速 PCB 信號(hào)線(xiàn)上的串?dāng)_。

串?dāng)_有兩種類(lèi)型;垂直和水平。垂直串?dāng)_是由其他層或?qū)娱g的信號(hào)引起的,而同層或?qū)觾?nèi)的信號(hào)則負(fù)責(zé)水平串?dāng)_。

注意:最大串?dāng)_值是接收器的預(yù)期電壓與接收器閾值之間的差值。

3.1 高速PCB設(shè)計(jì)中的串?dāng)_控制

可以通過(guò)分離走線(xiàn)、在各層之間放置接地層以及使用低介電材料來(lái)防止串?dāng)_。

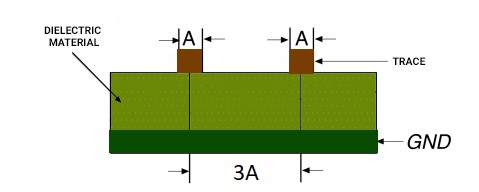

3.1.1 走線(xiàn)間距:兩條走線(xiàn)的中心間距至少應(yīng)為走線(xiàn)寬度的 3 倍。在不干擾兩條走線(xiàn)之間的間隔的情況下,將走線(xiàn)和接地層之間的距離減少到10 密耳有助于減輕串?dāng)_。

走線(xiàn)分離可以減少高速 PCB 中的串?dāng)_。

3.1.2 實(shí)心地平面的放置:可以通過(guò)在不同層之間放置實(shí)心地平面來(lái)防止不同層之間的串?dāng)_。雖然增加平面會(huì)增加成本,但它們解決了 SI 問(wèn)題,如控制走線(xiàn)阻抗、減少旁路電容電流環(huán)路和電源阻抗等。

實(shí)心接地層可以解決高速 PCB 中的信號(hào)完整性問(wèn)題。

3.1.3 低介電常數(shù)材料:低介電常數(shù)材料通過(guò)減少走線(xiàn)之間的互電容/雜散電容來(lái)克服串?dāng)_。

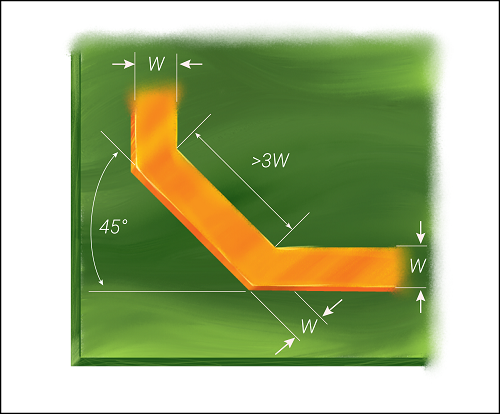

4. 高速PCB設(shè)計(jì)中直角走線(xiàn)和過(guò)孔的影響

走線(xiàn)布線(xiàn)和過(guò)孔位置會(huì)通過(guò)增加反射、串?dāng)_和改變阻抗值來(lái)影響信號(hào)完整性。具有直角的走線(xiàn)會(huì)導(dǎo)致更多輻射,因?yàn)樗鼤?huì)增加拐角區(qū)域的電容值,從而導(dǎo)致特性阻抗發(fā)生變化,隨后發(fā)生反射。

解決方案:可以通過(guò)用兩個(gè) 45 度角替換直角彎曲來(lái)最小化反射。為了獲得最小的阻抗變化,圓彎曲布線(xiàn)是最好的。

在拐角處,高速信號(hào)應(yīng)由 45° 彎曲代替。

過(guò)孔對(duì)于布線(xiàn)很重要,但包括它們會(huì)增加電感和電容值。這會(huì)改變特征阻抗值,增加反射。

過(guò)孔也會(huì)增加走線(xiàn)長(zhǎng)度。避免在不同的走線(xiàn)上添加過(guò)孔。

5. 高速PCB設(shè)計(jì)中不同布線(xiàn)技術(shù)的使用

正交布線(xiàn)以在不同層上引導(dǎo)信號(hào)并最小化耦合區(qū)域。

最小化信號(hào)之間的平行運(yùn)行長(zhǎng)度 (>500 mils)。僅具有短并行運(yùn)行的路線(xiàn)。

減少驅(qū)動(dòng)器扇出(負(fù)載數(shù)量)

6. 開(kāi)關(guān)效應(yīng):高速PCB設(shè)計(jì)中的地彈

與模擬不同,數(shù)字電路需要快速的開(kāi)關(guān)時(shí)間,因?yàn)樗梢栽凇?”和“1”以及“1”和“0”信號(hào)電平之間切換。當(dāng)速度增加時(shí),開(kāi)關(guān)周期減少。當(dāng)多個(gè)輸出同時(shí)從“高”邏輯切換到“低”時(shí),存儲(chǔ)在 I/O 負(fù)載電容中的電荷流入器件。該電流通過(guò)對(duì)地具有阻抗的引腳通過(guò)內(nèi)部地離開(kāi)設(shè)備。開(kāi)關(guān)電流在該阻抗中產(chǎn)生電壓。因此,器件和電路板地之間存在電壓差。這種電壓差稱(chēng)為地彈。地彈導(dǎo)致電路板上的其他設(shè)備將“低”輸出視為“高”。可以通過(guò)采用以下解決方案來(lái)減少地彈:

引腳壓擺率控制(允許設(shè)計(jì)人員減慢驅(qū)動(dòng)器的速度,從而降低跳動(dòng)率)。快速壓擺率負(fù)責(zé)反射、串?dāng)_和地彈;這就是為什么它的減少是必須的。

提供多個(gè)電源和接地引腳(允許將高速 I/O 引腳靠近接地引腳以減輕開(kāi)關(guān)效應(yīng))。

6.1 高速 PCB 中降低地彈的設(shè)計(jì)考慮

在處理 PCB 中的高速信號(hào)時(shí),設(shè)計(jì)人員應(yīng)考慮以下設(shè)計(jì)注意事項(xiàng):

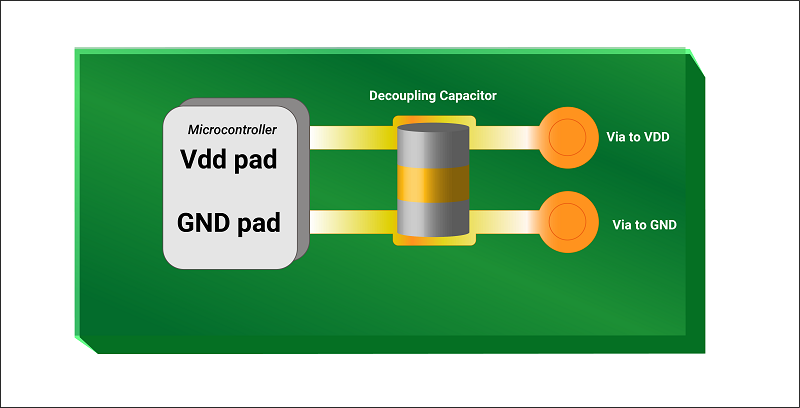

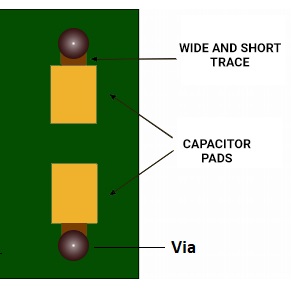

為相應(yīng)的 VCC/GND 對(duì)添加去耦電容。添加去耦電容器盡可能靠近器件的電源和接地引腳。如果電源和 GND 通過(guò)過(guò)孔到達(dá)引腳,則去耦電容器應(yīng)放置在引腳和過(guò)孔之間。

通過(guò)將去耦電容器靠近 IC 電源引腳放置,可以降低電源軌噪聲。

在輸出端添加外部緩沖器以最小化器件引腳上的負(fù)載。

通過(guò)使用外部設(shè)備(例如緩沖 IC)緩沖負(fù)載來(lái)控制負(fù)載電容。

最大限度地減少可以同時(shí)切換的輸出數(shù)量,并在整個(gè)設(shè)備中均勻分布。

盡可能去除上拉電阻(使用下拉電阻)。

使用提供獨(dú)立 VCC 和接地層的多層 PCB。

開(kāi)發(fā)同步設(shè)計(jì)。這種設(shè)計(jì)不會(huì)受到瞬時(shí)引腳切換的影響。

實(shí)現(xiàn)更大的通孔尺寸以將電容器焊盤(pán)連接到電源和接地層,以降低去耦電容器中的電感。

將過(guò)孔放置在靠近電容器墊的位置。

靠近電容焊盤(pán)放置通孔可以減少地彈。

使用表面貼裝電容器來(lái)最小化引線(xiàn)電感。

注意:通過(guò)電源層提供均勻分布的電源可以降低系統(tǒng)噪聲。

另請(qǐng)閱讀:復(fù)合放大器的優(yōu)缺點(diǎn)

7. 高速 PCB 設(shè)計(jì)中的 EMI 降低

PCB 還會(huì)影響系統(tǒng)的 EMI/EMC 性能。自動(dòng)布線(xiàn)板一般遵守設(shè)計(jì)規(guī)則(DRC),不滿(mǎn)足電磁兼容性要求。此類(lèi)板需要固定件,例如電纜和屏蔽外殼上的鐵氧體。這就是為什么始終建議確保正確放置組件并優(yōu)化布線(xiàn)的原因。它有助于實(shí)現(xiàn)在給定預(yù)算內(nèi)按時(shí)滿(mǎn)足所有電磁兼容性和信號(hào)完整性要求的產(chǎn)品。設(shè)計(jì)一個(gè)電磁兼容的 PCB 可以提高整個(gè)系統(tǒng)的性能。了解有關(guān)EMI 和 EMC 的 PCB 設(shè)計(jì)指南的更多信息。

每個(gè) PCB 都容易受到電磁干擾。可以通過(guò)以下方式減少:

使用低電感元件,例如具有低 ESR 和有效串聯(lián)電感 (ESL) 的表面貼裝電容器。

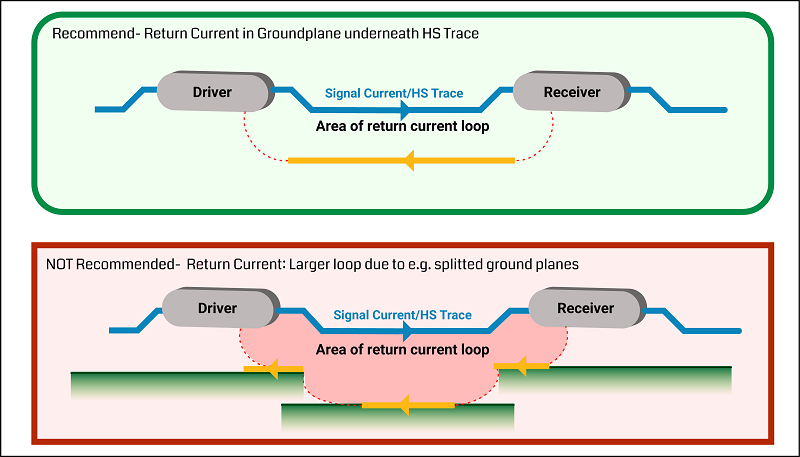

提供適當(dāng)?shù)慕拥匾詫?shí)現(xiàn)最短的電流返回路徑和最短的電流回路。

較短的返回路徑具有較低的阻抗,從而提供更好的 EMC 性能。

始終在電源/信號(hào)平面旁邊使用堅(jiān)固的接地平面。

高速 PCB 設(shè)計(jì)人員的快速提示

識(shí)別最高頻率網(wǎng)絡(luò)并計(jì)算系統(tǒng)中的最快上升時(shí)間。

檢查接收器和源的輸入和輸出處的電氣規(guī)格。

考慮走線(xiàn)上的受控阻抗值、端接和傳播延遲。閱讀為什么受控阻抗真的很重要?

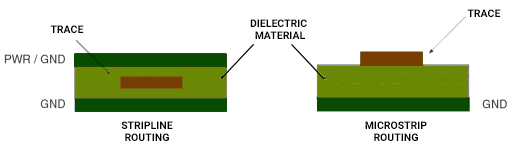

選擇微帶線(xiàn)(指在 PCB 外層布線(xiàn),由電介質(zhì)與參考平面(GND 或 VCC)隔開(kāi))和帶狀線(xiàn)(指在具有兩個(gè)參考平面的內(nèi)層布線(xiàn))布線(xiàn)技術(shù)。模擬確定哪種方法更符合 EMC 并且可以提供更好的信號(hào)完整性結(jié)果?

信號(hào)通過(guò)帶狀線(xiàn)和微帶布線(xiàn)傳輸。

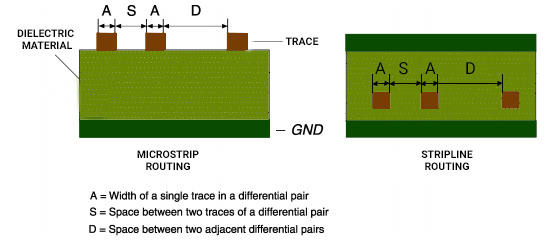

對(duì)于高質(zhì)量的信號(hào)傳輸,還要考慮時(shí)鐘和差分路由技術(shù)。

信號(hào)通過(guò)差分路由傳輸。

考慮不同電源電壓的數(shù)量。他們有自己的電源平面,還是可以拆分它們?

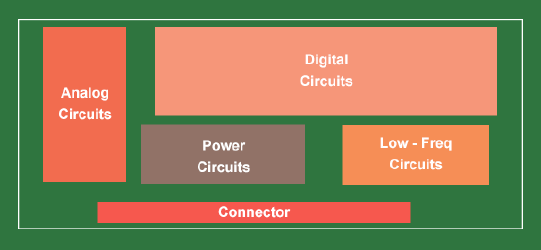

為發(fā)射器路徑、接收器路徑、模擬信號(hào)、數(shù)字信號(hào)等功能組創(chuàng)建圖表。

區(qū)分高速和低速信號(hào)。

至少兩個(gè)獨(dú)立的功能組之間是否存在任何互連?注意它們并始終考慮到其他走線(xiàn)的返回電流和串?dāng)_。

考慮空間寬度間隙。

兩層之間的最小距離應(yīng)該是多少?

鉆孔和通孔的最低要求是什么?使用盲埋孔是否可行?

高速PCB材料

最常用的層壓材料是 FR-4。只要電路板頻率保持在 2.5 到 3 GHz 的范圍內(nèi),它就非常具有成本效益。在高速下,Rogers RO4350 等材料比 FR-4 具有更好的性能。唯一的權(quán)衡是成本。非 FR-4 材料價(jià)格昂貴。

信號(hào)通過(guò) PCB 的速度取決于 PCB 的介電常數(shù)。舉個(gè)例子:當(dāng)頻率超過(guò)5 GHz時(shí),F(xiàn)R-4的介電常數(shù)(4.7)下降到4。另一方面,Rogers RO4350的介電值保持恒定(3.5左右)直到15 GHz。如果 PCB 的介電常數(shù)隨頻率不斷變化,則信號(hào)的不同頻率分量將獲得不同的速度,并在不同的時(shí)間到達(dá)負(fù)載,從而導(dǎo)致信號(hào)失真。

為什么在高速 PCB 設(shè)計(jì)中包含設(shè)計(jì)模擬和檢查很重要?

信號(hào)完整性檢查對(duì)于保持設(shè)計(jì)透明度至關(guān)重要。如果在設(shè)計(jì)過(guò)程中沒(méi)有執(zhí)行它,那么一旦電路板建成,它就無(wú)法根除。有鑒于此,PCB 設(shè)計(jì)軟件自帶信號(hào)完整性檢查功能,可以?xún)?yōu)化 PCB 布局,將錯(cuò)誤降至最低。您想了解更多有關(guān)如何模擬通道以識(shí)別和解決信號(hào)完整性問(wèn)題的信息嗎?然后觀(guān)看我們的 Keysight 教程,了解解決信號(hào)完整性問(wèn)題的基礎(chǔ)知識(shí)。

在高速設(shè)計(jì)中,信號(hào)完整性以及設(shè)計(jì)過(guò)程中的 EMC 理解和實(shí)施起著重要作用。信號(hào)完整性就是識(shí)別和消除導(dǎo)致信號(hào)質(zhì)量從 PCB 上的一個(gè)點(diǎn)傳輸?shù)搅硪粋€(gè)點(diǎn)時(shí)降低的因素。當(dāng) PCB 以高頻運(yùn)行時(shí),信號(hào)完整性變得非常重要,因?yàn)樾盘?hào)上升時(shí)間很短。采用適當(dāng)?shù)亩私臃桨浮⑺p控制、串?dāng)_和地彈預(yù)防可以幫助設(shè)計(jì)人員實(shí)現(xiàn)可以在高頻下無(wú)縫工作的 PCB。此外,符合 EMI 標(biāo)準(zhǔn)的設(shè)計(jì)也是必不可少的。

- 2025-03-20怎么選擇深圳SMT貼片加工廠(chǎng)?

- 2025-02-20深圳SMT貼片加工如何計(jì)算報(bào)價(jià)?

- 2025-07-25工程師都在找:支持01005元件±0.02mm精度的PCBA代加工廠(chǎng)

- 2025-07-25從設(shè)計(jì)到量產(chǎn)一站式服務(wù)!專(zhuān)業(yè)PCBA代加工廠(chǎng)讓您省心又省錢(qián)

- 2025-07-24代工報(bào)價(jià)相差40%?一圖看懂優(yōu)質(zhì)PCBA工廠(chǎng)的‘真實(shí)成本’構(gòu)成

- 2025-07-24工程師必看:高難度HDI板加工,選對(duì)這5個(gè)參數(shù)良率提升90%

- 2025-07-24智能硬件老板警惕:劣質(zhì)PCBA讓您售后成本翻3倍!

- 2025-07-23這家PCBA代工廠(chǎng)竟能做到24小時(shí)極速打樣?揭秘軍工級(jí)品質(zhì)的‘快’秘訣!

- 2025-07-23BOM成本直降30%!這家代工廠(chǎng)的國(guó)產(chǎn)替代方案讓比亞迪/小米都點(diǎn)贊

- 2025-07-22無(wú)鉛焊接工藝難點(diǎn):如何解決高溫回流下的元器件立碑問(wèn)題?

- 1怎么選擇深圳SMT貼片加工廠(chǎng)?

- 2深圳SMT貼片加工如何計(jì)算報(bào)價(jià)?

- 3工程師都在找:支持01005元件±0.02mm精度的PCBA代加工廠(chǎng)

- 4從設(shè)計(jì)到量產(chǎn)一站式服務(wù)!專(zhuān)業(yè)PCBA代加工廠(chǎng)讓您省心又省錢(qián)

- 5代工報(bào)價(jià)相差40%?一圖看懂優(yōu)質(zhì)PCBA工廠(chǎng)的‘真實(shí)成本’構(gòu)成

- 6工程師必看:高難度HDI板加工,選對(duì)這5個(gè)參數(shù)良率提升90%

- 7智能硬件老板警惕:劣質(zhì)PCBA讓您售后成本翻3倍!

- 8這家PCBA代工廠(chǎng)竟能做到24小時(shí)極速打樣?揭秘軍工級(jí)品質(zhì)的‘快’秘訣!

- 9BOM成本直降30%!這家代工廠(chǎng)的國(guó)產(chǎn)替代方案讓比亞迪/小米都點(diǎn)贊

- 10無(wú)鉛焊接工藝難點(diǎn):如何解決高溫回流下的元器件立碑問(wèn)題?