導致PCB信號完整性問題的 9 個因素

- 發表時間:2021-06-16 15:23:41

- 來源:本站

- 人氣:706

避免 PCB 中的信號完整性問題對設計人員來說是一項極其復雜的任務。它需要深入了解信號完整性設計規則和技術。隨著更快邏輯系列的推出,設計人員已經意識到簡單的 PCB 布局無法滿足信號完整性要求。

高速設計帶有特殊的信號完整性問題,如果處理不當,可能會讓您頭疼。始終建議工程師考慮某些最佳PCB 設計服務,以最大限度地減少早期設計周期中的信號完整性問題,從而避免昂貴的設計迭代。

隨著我們的繼續,我們將提供有關以下主題的更多見解:

什么是 PCB 中的信號完整性?

PCB 中的信號完整性需求

導致 PCB 信號完整性問題的 9 個因素

什么是 PCB 中的信號完整性?

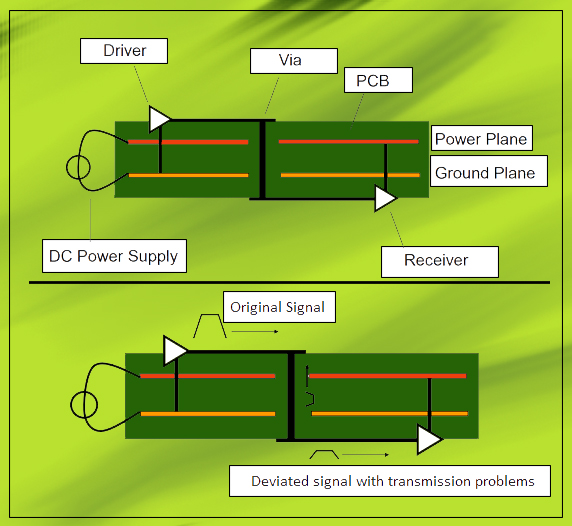

信號完整性 (SI) 表示信號無失真傳播的能力。信號完整性只不過是通過傳輸線的信號質量。當信號從驅動器傳輸到接收器時,它給出了信號衰減量的測量值。這個問題在較低頻率下不是主要問題,但當 PCB 以更高速度和高頻 (> 50MHz) 運行時,這是一個需要考慮的重要因素。在高頻狀態下,信號的數字和模擬方面都需要處理。

傳輸介質對信號完整性的影響。

當信號從驅動器傳播到接收器時,它不會保持不變,最初發送的任何內容都會以不同程度的失真被接收。這種信號失真是由阻抗失配、反射、振鈴、串擾、抖動和地彈等因素造成的。設計人員的主要目標應該是盡量減少這些因素,以便原始信號能夠以最小的失真到達目的地。還需要特別注意保持信號質量并控制它們在電子電路中的不良影響。閱讀我們關于使用 Altium 控制阻抗路由的文章。

PCB 中的信號完整性需求

當我們在 PCB 中遇到信號完整性問題時,它可能無法按預期工作。它可能以不可靠的方式工作——有時有效,有時無效。它可能在原型階段工作,但在批量生產中經常失敗;它可以在實驗室中工作,但在現場不可靠;它在舊的生產批次中工作,但在新的生產批次中失敗,等等。在以下情況下,信號已失去完整性:

它被扭曲,即它的形狀從所需的形狀改變

不需要的電噪聲疊加在信號上,降低了其信噪比 (S/N)

它會為板上的其他信號和電路產生不需要的噪聲

在以下情況下,PCB 被認為具有必要的信號完整性:

其內的所有信號均無失真傳播

其設備和互連不會受到來自其附近其他電氣產品的外來電噪聲和電磁干擾 (EMI) 的影響,符合或優于監管標準

它不會在連接到它或其附近的其他電路/電纜/產品中產生、引入或輻射 EMI,符合或優于監管標準

導致 PCB 中信號完整性下降的因素:

一般來說,快速的信號上升時間和高信號頻率會增加信號完整性問題。出于分析目的,我們可以將各種信號完整性問題分為以下幾類:

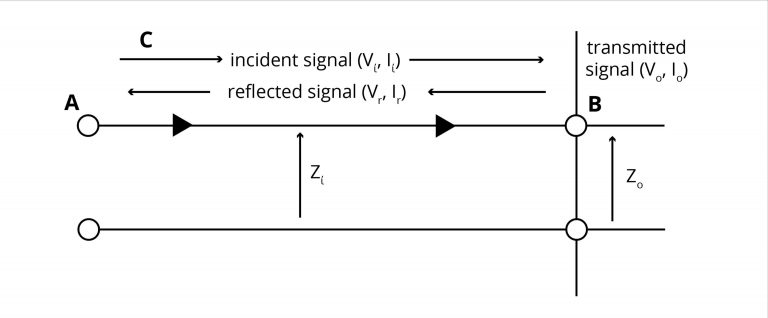

1. 不受控制的線路阻抗導致信號衰減

網絡上的信號質量取決于信號走線的特性及其返回路徑。在線路上傳輸過程中,如果信號遇到線路阻抗的變化或不均勻,它會受到反射,引起振鈴和信號失真。

此外,信號上升時間越快,不受控制的線路阻抗變化引起的信號失真就越大。我們可以通過以下方式減少或消除線路阻抗變化,從而最大限度地減少由于反射引起的信號失真:

確保信號線及其返回路徑充當具有統一受控阻抗的統一傳輸線。

將信號返回路徑作為靠近信號層放置的統一平面。

確保受控阻抗信號線看到匹配的源阻抗和接收器阻抗——與信號線的特征阻抗相同。這可能需要在源端和接收器端添加適當的終端電阻。

2. 由于其他阻抗不連續性導致的信號劣化

阻抗不連續會導致振鈴和信號失真。

正如我們之前提到的,如果信號在其傳播過程中遇到阻抗不連續,它將遭受反射,從而導致振鈴和信號失真。在遇到以下情況之一時,線路阻抗將出現不連續性:

當信號在其路徑中遇到過孔時。

當一個信號分支成兩條或更多條線時。

當信號返回路徑平面遇到不連續性時,例如當線路短截線連接到信號線時平面中的分裂。

當線路短截線連接到信號線時。

當信號線從源端開始時。

當信號線在接收端終止時。

當信號和返回路徑連接到連接器引腳時。

而且,信號上升時間越快,由阻抗不連續引起的信號失真就越大。我們可以通過以下方式最大限度地減少由于線路阻抗不連續引起的信號失真:

通過使用較小的微過孔和 HDI PCB 技術,最大限度地減少由過孔和過孔短截線引起的不連續性的影響。

減少跟蹤存根長度。

當一個信號在多個地方使用時,以菊花鏈方式布線而不是多點分支。

在源端和接收端使用合適的終端電阻。

使用差分信號和緊密耦合的差分對,它們本質上更不受信號返回路徑平面不連續性的影響。

確保在發生不連續的連接器處,信號線盡可能短,信號返回路徑盡可能寬。

3. 傳播延遲導致信號劣化

信號在 PCB 上從源傳輸到接收器所需的時間有限。信號延遲與信號線長度成正比,與特定 PCB 層上的信號速度成反比。如果數據信號和時鐘信號與整體延遲不匹配,它們將在不同的時間到達接收器進行檢測,這會導致信號偏移;過大的偏斜會導致信號采樣錯誤。隨著信號速度變得更高,采樣率也更高,并且允許的偏斜變得更小,由于偏斜導致更大的錯誤傾向。

提示:可以通過信號延遲匹配(主要是走線長度匹配)來最小化一組信號線中的歪斜。

4. 信號衰減導致信號衰減

由于傳導跡線電阻(由于趨膚效應在較高頻率下會增加)和介電材料損耗因數 Df 引起的損耗,信號在 PCB 線路上傳播時會遭受衰減。這兩種損耗都隨著頻率的增加而增加,因此信號的高頻分量將比低頻分量遭受更大的衰減;這會導致信號帶寬降低,進而導致信號上升時間增加導致信號失真;過度的信號上升時間增加導致數據檢測錯誤。

提示:當信號衰減是一個重要的考慮因素時,必須選擇正確類型的低損耗高速材料并適當控制走線幾何形狀以最大限度地減少信號損耗。

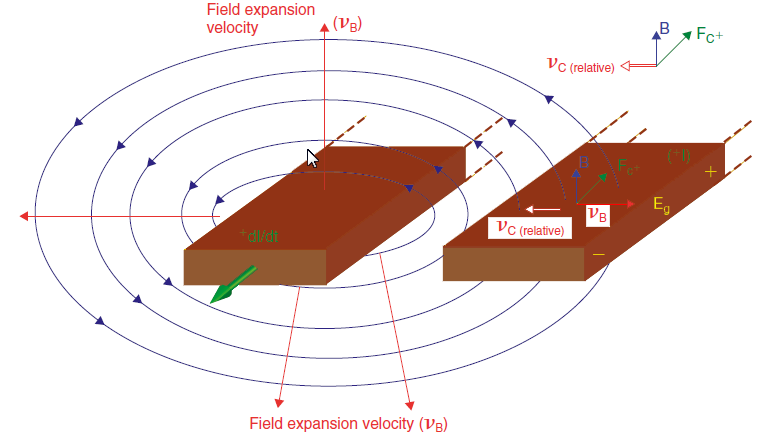

5.串擾噪聲導致信號劣化

相鄰 PCB 信號線上的串擾。

信號線或返回路徑平面上的快速電壓或電流轉換可能會耦合到相鄰的信號線上,從而在相鄰的信號線上導致稱為串擾和開關噪聲的不需要的信號。由于走線之間的互電容和互感而發生耦合。可以通過增加走線之間的空間來減少這種互電容和電感耦合。根據經驗,空間應該是走線寬度 (3W) 的三倍。與往常一樣,更快的上升時間信號會產生更多的串擾和開關噪聲。

串擾和開關噪聲可以通過以下方式降低:

增加相鄰信號走線之間的間隔。

使信號返回路徑盡可能寬,并且像統一平面一樣均勻,并避免分裂返回路徑。

使用介電常數較低的 PCB 材料。

使用差分信號和緊密耦合的差分對,它們本質上更不受串擾的影響。

6. 電源和地面分配網絡導致的信號衰減

電源和接地軌或路徑或平面具有非常低但有限的非零阻抗。當輸出信號和內部柵極切換狀態時,通過電源和接地軌/路徑/平面的電流會發生變化,從而導致電源和接地路徑中的電壓下降。這將降低設備電源和接地引腳上的電壓。這種情況的頻率越高,信號轉換時間越快,并且同時切換狀態的線路數量越多,電源和接地軌上的電壓下降就越大。這將降低信號的噪聲容限,如果過多,則會導致設備出現故障。

為了減少這些影響,配電網絡的設計必須使電力系統的阻抗最小化:

電源層和接地層應盡可能靠近并盡可能靠近 PCB 表面。這將減少通孔電感。

應在電源和接地軌之間使用多個低電感去耦電容器,并且它們應盡可能靠近器件電源和接地引腳放置。

使用帶有短引線的器件封裝。

為電源和接地使用薄的高電容磁芯可顯著增加電容并降低電源和接地軌之間的阻抗。閱讀我們如何減少 PCB 布局中的寄生電容。

7. EMI/EMC 導致的信號衰減

EMI/EMC 隨著頻率和更快的信號上升時間而增加。對于單端信號電流,輻射遠場強度隨頻率線性增加,與差分信號電流成正比。閱讀EMI 和 EMC 的 PCB 設計指南以獲取詳細說明。

提示:也可以通過減小電流環路面積來降低 EMI。

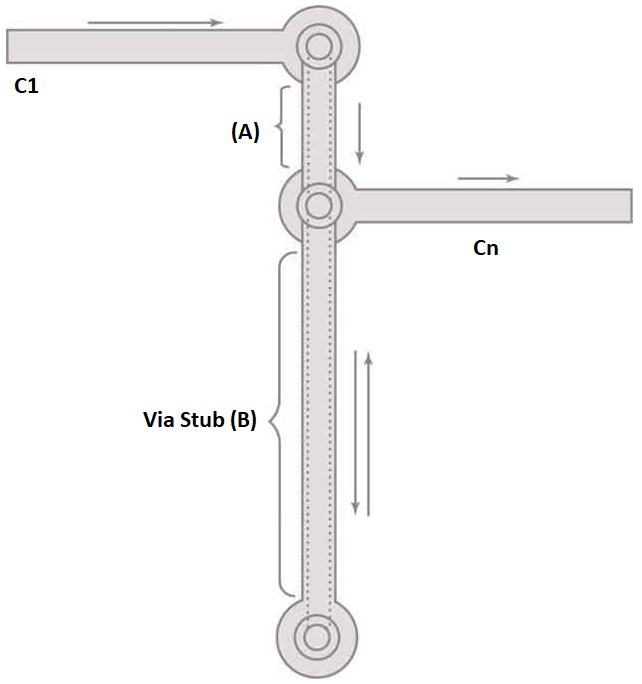

8. 由于via stub 和trace stub 導致的信號完整性問題

過孔存根是不用于信號傳輸的過孔部分。過孔短截線充當具有特定諧振頻率的諧振電路,在該頻率下它可以在其中存儲最大能量。如果信號在該頻率處或附近具有顯著分量,則該信號分量將由于通孔短截線在其諧振頻率處的能量需求而嚴重衰減。在下面描述的示例中,通孔的部分A用于從外層上的導體C1到內層上的導體Cn 的信號傳播。但通孔的B部分是無關緊要的——因此,是通孔存根。在此處了解有關過孔存根及其對信號衰減和數據傳輸速率的影響的更多信息。

Via stub 導致 PCB 中的嚴重信號衰減。

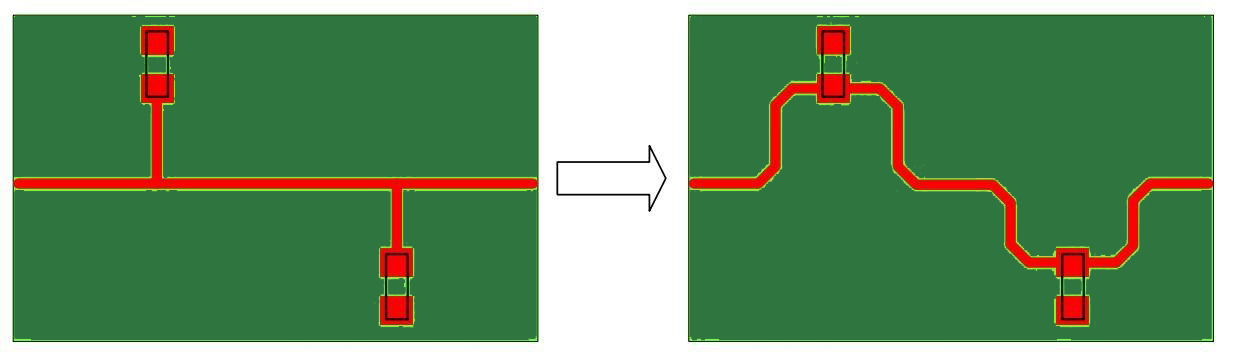

長短線跡線可能充當天線,因此會增加遵守 EMC 標準的問題。短線跡線還會產生反射,對信號完整性產生負面影響。高速信號上的上拉或下拉電阻是短線的常見來源。如果需要此類電阻器,則將信號路由為菊花鏈。

通過實施菊花鏈路由避免存根跟蹤。

9. 地彈引起的信號完整性問題

由于電流過大,電路的接地參考電平偏離了原來的電平。這是由于接地電阻和互連電阻(例如鍵合線和跡線)造成的。因此,地中不同點的地電壓電平會有所不同。這被稱為接地反彈,因為接地電壓會隨電流而變化。

減少地彈的技巧:

實現去耦電容到本地接地。

包含串聯的限流電阻。

將去耦電容器靠近引腳放置。

運行適當的地面。

信號的上升時間是 SI 問題中的一個關鍵參數。為了獲得所需的信號完整性水平,我們應該關注阻抗控制、衰減、地彈、傳播延遲和 EMI/EMC。在 PCB 的設計階段應采取信號完整性措施,因為我們不能時不時地提出新設計。最好事先處理它,而不是讓它實時破壞設備的性能。查看有關如何實現穩健的 PCB 設計工作流程以實現信號完整性的帖子?收集有關 PCB 設計信號完整性的更多信息。

【上一篇:】PCB傳輸線的損耗

【下一篇:】PCB設計中高速信號的影響

- 2025-03-20怎么選擇深圳SMT貼片加工廠?

- 2025-02-20深圳SMT貼片加工如何計算報價?

- 2025-06-27軍工級PCBA后焊特殊要求:三防漆涂覆前的清潔度檢測標準

- 2025-06-27自動化替代人工?選擇性波峰焊在插件后焊中的效率與成本對比分析

- 2025-06-26綠色組裝趨勢:無鉛焊接與可降解包裝在PCBA成品組裝中的應用

- 2025-06-26小家電PCBA加工的“高性價比”密碼:如何平衡成本與可靠性?

- 2025-06-26PCBA成品組裝的散熱設計:導熱硅膠、散熱片與風道的協同優化

- 2025-06-25PCBA成品組裝的“零缺陷”挑戰:如何實現99.9%直通率?

- 2025-06-25汽車電子PCBA代工首選:潤澤五洲如何通過IATF 16949認證的12項嚴苛測試?

- 2025-06-24智能硬件PCBA的核心挑戰:如何平衡微型化設計與散熱性能?

- 1怎么選擇深圳SMT貼片加工廠?

- 2深圳SMT貼片加工如何計算報價?

- 3軍工級PCBA后焊特殊要求:三防漆涂覆前的清潔度檢測標準

- 4自動化替代人工?選擇性波峰焊在插件后焊中的效率與成本對比分析

- 5綠色組裝趨勢:無鉛焊接與可降解包裝在PCBA成品組裝中的應用

- 6小家電PCBA加工的“高性價比”密碼:如何平衡成本與可靠性?

- 7PCBA成品組裝的散熱設計:導熱硅膠、散熱片與風道的協同優化

- 8PCBA成品組裝的“零缺陷”挑戰:如何實現99.9%直通率?

- 9汽車電子PCBA代工首選:潤澤五洲如何通過IATF 16949認證的12項嚴苛測試?

- 10智能硬件PCBA的核心挑戰:如何平衡微型化設計與散熱性能?