Ripple Carry Adder:您需要知道的一切

- 發(fā)表時(shí)間:2021-10-12 09:50:53

- 來(lái)源:本站

- 人氣:1325

邏輯電路可以依靠紋波進(jìn)位加法器將 n 位值加在一起。因此,這種數(shù)字電路實(shí)現(xiàn)在許多應(yīng)用中提供了有用的功能。然而,由于計(jì)算過(guò)程緩慢,它也表現(xiàn)出延遲的性能。這通常涉及等待每個(gè)全加器級(jí)將位紋波到下一個(gè)全加器級(jí)。這樣的過(guò)程不斷重復(fù),直到結(jié)束,提供結(jié)果。

理解紋波進(jìn)位加法器似乎有點(diǎn)令人困惑。考慮到這一點(diǎn),我們將這篇文章放在一起,以幫助您獲得有關(guān)此主題的更多知識(shí)。讓我們開始吧!

什么是波紋進(jìn)位加法器?

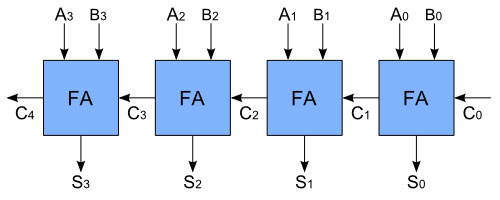

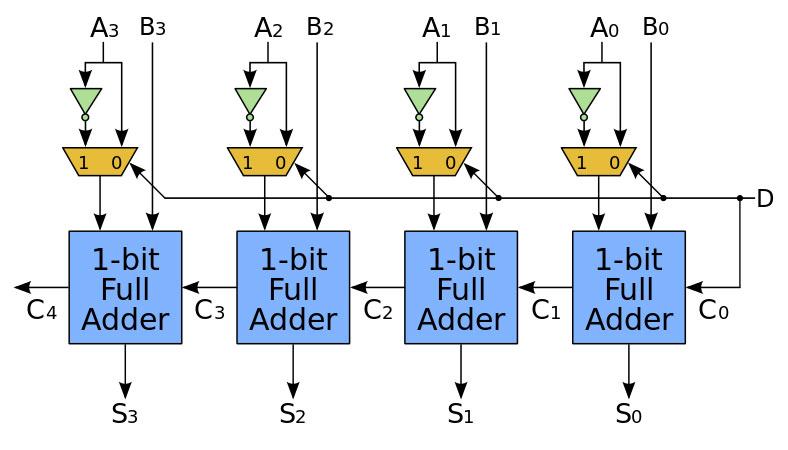

紋波進(jìn)位加法器用作數(shù)字電路,將兩個(gè)二進(jìn)制 n 位數(shù)字相加并提供結(jié)果。它的結(jié)構(gòu)由幾個(gè)全加器組成,每個(gè)全加器以級(jí)聯(lián)設(shè)置連接。以這種方式,全加器的進(jìn)位輸出連接到下一個(gè)全加器輸入。

4 位紋波攜帶加法器的示意圖。

資料來(lái)源:維基共享資源

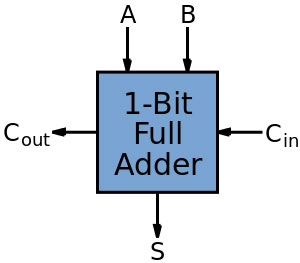

全加器代表一個(gè)邏輯電路,旨在將三個(gè)輸入相加,同時(shí)生成兩個(gè)輸出。更具體地說(shuō),兩個(gè)輸入用作 A 和 B,而第三個(gè)輸入表示一個(gè)進(jìn)位位。(C-IN) 同時(shí),一個(gè)輸出代表進(jìn)位輸出位(C-OUT),另一個(gè)代表求和位(S)。最終,全加器電路可以連接到八個(gè)輸入以形成一個(gè)字節(jié)寬的加法器。這將一個(gè)進(jìn)位位從一個(gè)加法器級(jí)聯(lián)到下一個(gè)。將兩個(gè)半加器電路連接在一起將形成一個(gè)全加器。

一個(gè)完整的加法器邏輯圖

資料來(lái)源:維基共享資源

紋波進(jìn)位加法器工作原理

每個(gè)進(jìn)位通過(guò)一個(gè)全加器級(jí)生成,然后通過(guò)其輸入進(jìn)入下一個(gè)全加器。整個(gè)過(guò)程繼續(xù)進(jìn)行,直到到達(dá)最終的全加器。結(jié)果,每個(gè)進(jìn)位輸出位波紋到下一個(gè)全加器級(jí)。總的來(lái)說(shuō),最關(guān)鍵的操作是將每個(gè)輸入位序列加在一起,例如 4 位加法器、8 位加法器、16 位加法器等。

由于邏輯電路的傳播延遲,在進(jìn)位階段結(jié)束之前,總和和進(jìn)位位保持無(wú)效。由于輸入和輸出之間經(jīng)過(guò)的時(shí)間量,通常會(huì)發(fā)生傳播延遲。例如,當(dāng)非門輸入設(shè)置為 0 時(shí),輸出將配置為 1,等等。傳播延遲定義了輸出設(shè)置為零和輸入配置為 1 之間經(jīng)過(guò)的時(shí)間。此外,進(jìn)位傳播延遲定義了接收進(jìn)位信號(hào)和執(zhí)行進(jìn)位信號(hào)之間經(jīng)過(guò)的時(shí)間。

波紋進(jìn)位加法器真值表

的真值表,如下所示,確定用于在一個(gè)脈動(dòng)進(jìn)位加法器的所有輸入中的每個(gè)輸出值。

漣漪帶有加法器真值表。

波紋進(jìn)位加法器 VHDL 代碼和 Verilog 代碼

要實(shí)現(xiàn)紋波進(jìn)位加法器,您將需要VHDL 代碼和 Verilog 代碼。提供了兩個(gè)示例。第一個(gè)涉及兩位紋波進(jìn)位加法器。同時(shí),另一個(gè)示例產(chǎn)生一個(gè)紋波進(jìn)位加法器,它收集每個(gè)輸入寬度作為參數(shù)。

紋波進(jìn)位加法器應(yīng)用

時(shí)鐘包含一個(gè)紋波進(jìn)位加法器

對(duì)兩個(gè) N 位值執(zhí)行加法

數(shù)字信號(hào)處理和微處理器

計(jì)時(shí)器

計(jì)算器

時(shí)鐘

Ripple Carries Adder的優(yōu)缺點(diǎn)

好處

紋波進(jìn)位加法器并不昂貴。

資料來(lái)源:維基共享資源

通過(guò) n 位加法提供準(zhǔn)確的結(jié)果

簡(jiǎn)單的設(shè)計(jì)和開發(fā)過(guò)程

物美價(jià)廉

缺點(diǎn)

延遲會(huì)對(duì)其整體功能造成不便

它一次只允許一個(gè)全加器運(yùn)行

進(jìn)位延遲導(dǎo)致它運(yùn)行緩慢

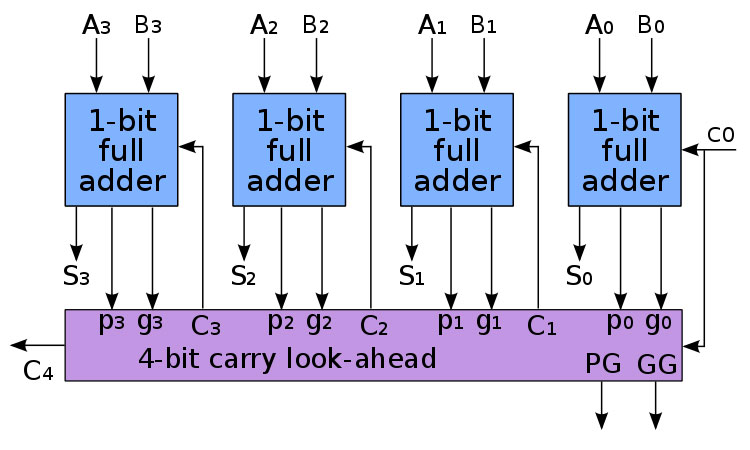

進(jìn)位前瞻加法器

進(jìn)位超前邏輯在達(dá)到總和之前計(jì)算進(jìn)位位,有效地減少了時(shí)間延遲。這發(fā)生在通過(guò)兩種方法生成進(jìn)位信號(hào)之后。第一個(gè)涉及等于 1 的 a 和 b 位。同時(shí),第二種方法涉及進(jìn)位和等于 1 的 a 或 b 位。這些位在前一級(jí)實(shí)現(xiàn),而進(jìn)位在加法器的開頭開始。

進(jìn)位前瞻加法器原理圖。

資料來(lái)源:維基共享資源

在紋波進(jìn)位加法器中,每個(gè)全加器在計(jì)算總和之前將進(jìn)位位處理到下一個(gè)加法器。因此,該過(guò)程會(huì)導(dǎo)致很長(zhǎng)的延遲。

概括

總的來(lái)說(shuō),進(jìn)位紋波加法器提供了在數(shù)字電路中將兩個(gè) n 位數(shù)字相加的能力。盡管過(guò)程緩慢,但它仍然具有有用的應(yīng)用程序,這些應(yīng)用程序本質(zhì)上有助于數(shù)字信號(hào)處理。以這種方式,紋波進(jìn)位加法器將進(jìn)位位紋波到每個(gè)全加器級(jí),直到它到達(dá)最后的全加器。此時(shí),它將執(zhí)行所需的計(jì)算。但是,進(jìn)位超前加法器可以更快地完成此計(jì)算,因?yàn)樗褂昧瞬煌募夹g(shù)。從而減少延遲時(shí)間。

您對(duì)紋波進(jìn)位加法器有任何疑問(wèn)嗎?請(qǐng)隨時(shí)與我們聯(lián)系!

【上一篇:】Ir Blaster:如何理解和使用IR Blaster

【下一篇:】鉛酸電池充電器電路-不同的充電策略

- 2025-03-20怎么選擇深圳SMT貼片加工廠?

- 2025-02-20深圳SMT貼片加工如何計(jì)算報(bào)價(jià)?

- 2025-06-26綠色組裝趨勢(shì):無(wú)鉛焊接與可降解包裝在PCBA成品組裝中的應(yīng)用

- 2025-06-26小家電PCBA加工的“高性價(jià)比”密碼:如何平衡成本與可靠性?

- 2025-06-26PCBA成品組裝的散熱設(shè)計(jì):導(dǎo)熱硅膠、散熱片與風(fēng)道的協(xié)同優(yōu)化

- 2025-06-25PCBA成品組裝的“零缺陷”挑戰(zhàn):如何實(shí)現(xiàn)99.9%直通率?

- 2025-06-25汽車電子PCBA代工首選:潤(rùn)澤五洲如何通過(guò)IATF 16949認(rèn)證的12項(xiàng)嚴(yán)苛測(cè)試?

- 2025-06-24智能硬件PCBA的核心挑戰(zhàn):如何平衡微型化設(shè)計(jì)與散熱性能?

- 2025-06-24高密度板加工挑戰(zhàn):PCBA一站式工廠如何同步實(shí)現(xiàn)0.1mm精度與72小時(shí)交付?

- 2025-06-24海外訂單專屬方案:一站式工廠的跨境PCBA生產(chǎn)如何保障交付穩(wěn)定性?

- 1怎么選擇深圳SMT貼片加工廠?

- 2深圳SMT貼片加工如何計(jì)算報(bào)價(jià)?

- 3綠色組裝趨勢(shì):無(wú)鉛焊接與可降解包裝在PCBA成品組裝中的應(yīng)用

- 4小家電PCBA加工的“高性價(jià)比”密碼:如何平衡成本與可靠性?

- 5PCBA成品組裝的散熱設(shè)計(jì):導(dǎo)熱硅膠、散熱片與風(fēng)道的協(xié)同優(yōu)化

- 6PCBA成品組裝的“零缺陷”挑戰(zhàn):如何實(shí)現(xiàn)99.9%直通率?

- 7汽車電子PCBA代工首選:潤(rùn)澤五洲如何通過(guò)IATF 16949認(rèn)證的12項(xiàng)嚴(yán)苛測(cè)試?

- 8智能硬件PCBA的核心挑戰(zhàn):如何平衡微型化設(shè)計(jì)與散熱性能?

- 9高密度板加工挑戰(zhàn):PCBA一站式工廠如何同步實(shí)現(xiàn)0.1mm精度與72小時(shí)交付?

- 10海外訂單專屬方案:一站式工廠的跨境PCBA生產(chǎn)如何保障交付穩(wěn)定性?