運算放大器遲滯:終極指南

- 發表時間:2021-10-08 09:45:44

- 來源:本站

- 人氣:1263

技術世界中的許多基本概念很難處理,因為它們的含義可能具有欺騙性。不幸的是,滯后是這些基本概念之一。

您可能已經嘗試過搜索概念,結果卻放棄或遇到了您想放棄的復雜而漫長的事情。但是,不用擔心,我們有解決方案!

幸運的是,我們寫這篇文章是為了將運算放大器遲滯的概念分解為一個簡單而全面的指南。

你準備好了嗎?那么,讓我們開始吧!

什么是運算放大器中的遲滯?

運算放大器圖

資料來源:維基共享資源

一旦我們定義了遲滯這個詞,運算放大器遲滯的話題就會開始變得有意義。簡而言之,滯后意味著落后或落后或抵制從前狀態的變化。另外,在工程中,滯后描述了非對稱操作,或者更簡單地說,從 A 到 B 的路徑與 B 到 A 不同。

更重要的是,您可以在磁性、非塑性變形以及運算放大器等電子電路(用作比較器)等領域找到滯后現象。

動態專用鎖存比較器

資料來源:維基共享資源

為了進一步分解,讓我們看一個簡單的示例,以幫助確定運算放大器中的滯后意味著什么。

當您將 12 伏繼電器連接到可變電源并從 0 到 12 緩慢增加輸入電源電壓時,您會注意到在 11 伏附近,繼電器將激活。

所以,通常,如果你降低這個電壓,它應該關閉繼電器。但是,事實并非如此。只有當電壓遠低于 9 伏時,繼電器才會關閉。

現在繼電器的激活和停用閾值之間的差異就是我們所說的電壓滯后。這種電壓滯后就是我們所說的遲滯。

現在,遲滯會對電子電路(如單個 BJT 電路)產生負面影響。它可以防止您在電路上保持任何固定的閾值水平。

因此,大多數情況下,滯后水平會降低到可能的最小水平——以保持對電路閾值的控制。

相比之下,運算放大器電路在處理某些操作時可有效避免滯后效應。對于大多數運算放大器電池充電器電路,沒有遲滯成為一個很大的缺點。

因此,在這種情況下,您可以通過在運算放大器輸出端和其輸入引腳之一上安裝反饋電阻器來強制將額外的滯后作用到電路中。因此,這將有助于在您的運算放大器電路中包含遲滯效應。

另一方面,大多數比較器都帶有內置遲滯。這些比較器的值通常在 5mV 到 10mV 之間。此外,這些模擬比較器的內部遲滯有助于它們防止因極少量寄生反饋引起的振蕩。

然而,任何更大幅度的外部噪聲都可以阻止這些比較器的內部遲滯,即使它足以阻止自振蕩。在這種情況下,只需包含外部滯后就可以解決問題。

工作原理

盡管在某些電路中不需要遲滯,但它在模擬電路中仍然有用,因為它有助于控制帶有晶體管的電路中的開關。因此,您可以在比較器電路中使用遲滯來設置輸出波形的占空比。

注意:運算放大器和比較器是這些電路中兩個重要且同等的組件。更重要的是,運算放大器可以用作比較器,但并非所有比較器都可以用作放大器。

出于這個原因,這兩個術語可以互換使用,因為遲滯對兩個電路都很重要。此外,了解這些電路的工作原理對于了解遲滯在高級電路中的工作原理大有幫助。

現在,當您將兩個常見的集成電路與運算放大器和比較器進行比較時,可以更容易地理解遲滯在其中一些電路中的工作原理以及如何使用它來將這些電路的開關行為修改為您想要的。

兩種元件的 IC 比較

來源:快照

您從上圖中獲得的第一印象是這兩個組件的相似程度。但是,存在差異,例如比較器是接地發射器,而運算放大器則不是。出于這個原因,比較器的輸出在飽和狀態下工作良好。另一方面,運算放大器的輸出對于線性運算效果更好。

集成電路

比較器中的遲滯

實際比較器電路中的遲滯負責產生穩定的開關行為。當您添加正反饋電阻時,它會在電路中產生遲滯,從而在輸入信號增加或減少時設置切換閾值。

這是棘手的部分。

輸入信號上的雜散噪聲會影響整個過程。因此,隨著輸入信號的增加產生多個轉換。因此,在比較器電路中添加遲滯可以抵消由噪聲引起的任何錯誤切換。

運算放大器中的遲滯

運算放大器中的遲滯類似于正反饋如何在比較器中產生遲滯電壓(不是負電壓)。因此,這允許運算放大器形成施密特觸發電路。

這就是事情變得有趣的地方。

當您將作為閉環電路的運算放大器驅動到飽和(具有遲滯)時,輸出將飽和并為您提供與比較器相同的結果。它適用于反相輸入和非反相輸入。

無遲滯比較器

無遲滯比較器

來源:快照

這是一個沒有遲滯的標準比較器電路。對于該電路,分壓器網絡 Rx 和 Ry 創建課程使用的最小閾值電壓。因此,比較器會評估輸入電壓范圍 (Vin) 并將其與固定閾值電壓 (Vth) 進行比較,以找出電壓之間的關系。

現在,將輸入饋電電壓(您要比較)連接到電路的反相輸入端會產生極性反相的輸出。

因此,只要輸入偏置電流的電壓差比閾值更顯著,輸出就會靠近負電源。同樣,如果該點高于輸入參考電壓,則比較器輸出將更靠近正電源軌。

雖然這種技術有它的好處,比如確定信號是否高于設定的閾值,但它有一個問題。輸入信號上的噪聲會在固定點上方和下方產生多次轉換,從而觸發波動的結果。

無滯后比較器的輸出

來源:快照

您可以在上圖中看到多個轉換。想象一下,輸入信號是一個溫度參數,而輸出是一個關鍵的溫度應用程序,可以使事情變得更加透明。現在,不一致的輸出信號可能無法提供您想要的結果。

或者,假設您需要比較器的輸出來運行電機或閥門。在臨界閾值情況下,波動的信號會多次打開/關閉閥門。

幸運的是,這是 Hysteresis 解決的一個問題,因為它在切換閾值時完全抵消了不穩定的信號,并提供了一定的抗噪能力。

具有遲滯的比較器

具有遲滯的比較器電路

來源:快照

現在,這是帶有遲滯的比較器電路圖。此處,電阻器 RH 側重于滯后的閾值水平。因此,只要輸出電壓變為邏輯高 (5V),RH 就會與 Rx 并聯。因此,允許額外的直流電流流入 Ry 并將閾值 (VH) 限制增加到 2.7v。此外,如果輸入電流不高于閾值電壓 (2.7v),則輸出響應不會變為邏輯低。

然而,當輸出為邏輯低時,Rh 與 Ry 平行。因此,減少流入 Ry 的電流并降低閾值電壓 t0 2.3v。現在,要回到邏輯高電平 (5V),輸入信號必須低于 2.3 v。

磁滯比較器的設計

因此,為了分解遲滯比較器的設計,我們將查看原理圖、組件和設計。

示意圖

看看下面的圖表:

遲滯比較器電路原理圖

來源:快照

所需電子元件

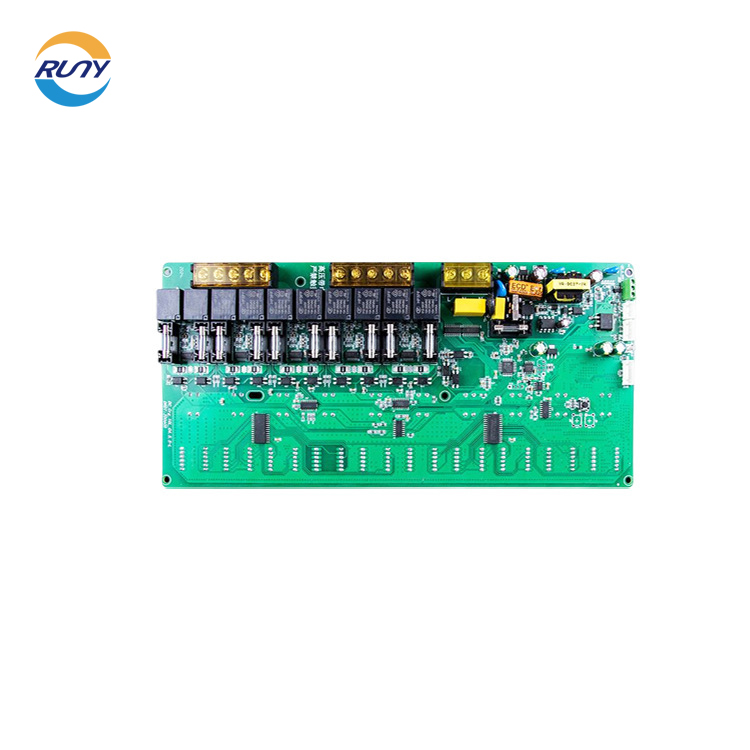

(1) 印刷電路板 ( PCB )

比較器(在這里,您可以使用任何比較器。例如,我們將 TLV3201 用于低功耗應用。該比較器具有低靜態電流)

標準金屬膜電阻器 (0.1%)

設計要求

+5v 電源電壓

0v 至 5v 輸入

遲滯比較器設計

遲滯比較器設計公式

來源:快照

對于設計,我們可以使用等式 (1) 和 (2) 來選擇電阻值以創建遲滯閾值電壓(即 VH 和 VL)。另外,您需要選擇具有單一值的 RX。

我們確定我們的 RX 將具有 100k 評級。我們選擇了這個額定值,以便 RX 可以最大限度地減少電流消耗。另一方面,我們使用 576k 值實現了 Rh。因此,我們確認了附錄 A 中的方程 (1) 和 (2):Rh/Rx = VL/VH – VL。

最后的話

比較器在區分兩個信號電平時很有用。例如,您可以使用比較器來區分正常和超溫條件。

此外,比較閾值處的噪聲或信號變化會導致多次轉換。因此,遲滯在比較器電路中的優勢在于它固定了一個下限和上限,以解決眾多轉換的問題。好吧,這篇文章到此結束;如果您有任何問題,請隨時與我們聯系。

【上一篇:】霓虹燈電路:它是什么以及它是如何工作的?

【下一篇:】藍牙接口:如何與藍牙模塊接口

- 2025-03-20怎么選擇深圳SMT貼片加工廠?

- 2025-02-20深圳SMT貼片加工如何計算報價?

- 2025-06-26綠色組裝趨勢:無鉛焊接與可降解包裝在PCBA成品組裝中的應用

- 2025-06-26小家電PCBA加工的“高性價比”密碼:如何平衡成本與可靠性?

- 2025-06-26PCBA成品組裝的散熱設計:導熱硅膠、散熱片與風道的協同優化

- 2025-06-25PCBA成品組裝的“零缺陷”挑戰:如何實現99.9%直通率?

- 2025-06-25汽車電子PCBA代工首選:潤澤五洲如何通過IATF 16949認證的12項嚴苛測試?

- 2025-06-24智能硬件PCBA的核心挑戰:如何平衡微型化設計與散熱性能?

- 2025-06-24高密度板加工挑戰:PCBA一站式工廠如何同步實現0.1mm精度與72小時交付?

- 2025-06-24海外訂單專屬方案:一站式工廠的跨境PCBA生產如何保障交付穩定性?

- 1怎么選擇深圳SMT貼片加工廠?

- 2深圳SMT貼片加工如何計算報價?

- 3綠色組裝趨勢:無鉛焊接與可降解包裝在PCBA成品組裝中的應用

- 4小家電PCBA加工的“高性價比”密碼:如何平衡成本與可靠性?

- 5PCBA成品組裝的散熱設計:導熱硅膠、散熱片與風道的協同優化

- 6PCBA成品組裝的“零缺陷”挑戰:如何實現99.9%直通率?

- 7汽車電子PCBA代工首選:潤澤五洲如何通過IATF 16949認證的12項嚴苛測試?

- 8智能硬件PCBA的核心挑戰:如何平衡微型化設計與散熱性能?

- 9高密度板加工挑戰:PCBA一站式工廠如何同步實現0.1mm精度與72小時交付?

- 10海外訂單專屬方案:一站式工廠的跨境PCBA生產如何保障交付穩定性?