如何限制 PCB 傳輸線中的阻抗不連續性和信號反射

- 發表時間:2021-06-21 16:04:51

- 來源:本站

- 人氣:989

我們之前在PCB 傳輸線文章中快速討論了信號反射。這是一篇關于PCB設計人員應該掌握的非常重要的主題的深入文章。首先要記住的是,由于阻抗不連續,PCB 傳輸線中會發生信號反射。

傳輸線應具有均勻的特性阻抗。阻抗的任何變化或不連續都會導致信號反射和失真。

這種現象同樣適用于 PCB 走線和傳輸線。原因是高頻信號的物理波長非常短。因此,PCB 走線表現出相同的特性。頻率越高,波長越短。您甚至必須像傳輸線一樣對待較短的走線。

信號軌跡不連續性或非均勻不連續性形成信號完整性不連續性。為了避免源端和目標端的信號失真,您必須將 PCB 走線阻抗與源端匹配。然后您必須在源端和目標端加載阻抗。這提出了一個相當大的挑戰,需要仔細的 PCB 設計來減輕由阻抗不連續引起的信號衰減的影響。特性阻抗的不連續性越大,信號反射就越高。這意味著信號失真也更高。因此,盡量保持阻抗不連續性盡可能小。在幅度和時間方面。閱讀:為什么受控阻抗真的很重要。

阻抗不連續性影響信號完整性

理論上,數字信號是在很短的時間內切換的方波脈沖。自然而然地,高頻數字電路所需的短信號上升時間將導致與快速信號上升時間相關的極高頻率。實際上,這些頻率將比電路的時鐘頻率高一個數量級。高頻數字電路的脈寬更短。從而更短的上升時間。非常短的信號上升時間意味著數字信號中包含非常高的頻率。因此,高頻數字信號應遵循與高頻信號相關的信號完整性規則。

因此,PCB 走線阻抗的任何變化都會導致信號反射。這些會導致振鈴和信號失真。這樣做的結果是,在高開關頻率下,阻抗不連續性對數字信號造成的失真非常嚴重,可能會出現信號采樣錯誤。您可以通過以下參數表征由 PCB 走線形成的傳輸線:電阻、電導和走線電阻。閱讀PCB 中微帶線和帶狀線的區別。

典型的阻抗不連續性

線路的特性阻抗是電感除以電容的平方根。這是 PCB 的合理假設,因為與其電感和電容相比,高信號頻率下的走線電阻和電導可以忽略不計。

阻抗不連續是任何影響走線電感與其電容之比的因素。下面是一些典型的例子:

線路中的阻抗變化:如果線路的阻抗因任何原因發生變化,例如由于銅截面的變化或走線路徑的變化,互感會發生變化,并且會出現阻抗不連續。

線路中的分支:雖然可能需要將信號路由到多個設備,但分支和線路短截線的使用會改變線路阻抗,從而導致不連續。

返回信號分裂:高頻信號沿著阻抗最低的路徑傳播,該路徑位于信號走線的正下方,通常位于接地層中。返回線或接地平面中任何迫使返回信號偏離此路徑的物理特征都會造成不連續性。

過孔:使用過孔將信號從 PCB 的一層傳輸到另一層。盡管是 PCB 設計的基本特征,但過孔的形狀和尺寸會改變走線的電感和電容,從而產生另一個不連續性。要了解更多信息,請閱讀如何減少 PCB 布局中的寄生電容。

如何限制阻抗不連續的影響

控制阻抗不連續性負面影響的關鍵是將所有 PCB 信號走線視為傳輸線。您應該確保信號路徑上所有點的特征阻抗都相同。

確保您遵循以下準則:

匹配源阻抗和負載阻抗:確保源阻抗和負載阻抗與走線阻抗相同。您可以通過使用串聯或并聯電阻來實現正確的阻抗來實現這一點。此外,您必須使用正確值的電阻器終止任何開路走線。

避免分支:如果信號必須由多個芯片共享,請以菊花鏈方式連接線路,而不是使用分支。或者,可以使用匹配的緩沖設備將信號傳輸到分支。

信號返回路徑:確保信號返回遵循與信號線相同的路徑。如果使用接地層,請確保沒有中斷返回信號路徑的分裂。確保走線下方有一個貫穿整個長度的實心平面,沒有裂口或切口。如果沒有實心平面,請使用較粗的返回走線,它應覆蓋走線縱向和電介質高度的三倍。

過孔設計:將高頻走線布置在盡可能遠的一層上。如果需要過孔,請使用微孔代替傳統的過孔。由于通孔具有顯著不同的電容和電感特性,因此盡量減少它們在信號走線上的使用。在需要的地方,使用電容和電感比標準過孔小得多的微過孔。微孔還有助于使存根長度盡可能短。另一種方法是使用高密度互連或HDI PCB技術。

阻抗不連續的不利影響是嚴重的。您不能在以高時鐘頻率運行的數字 PCB 電路中忽略它們。在通過遵循合理的設計實踐并在可能的情況下使用高級 PCB 設計軟件來評估和減少阻抗不連續性來控制這些影響時,您應該小心。

阻抗不連續性和信號反射

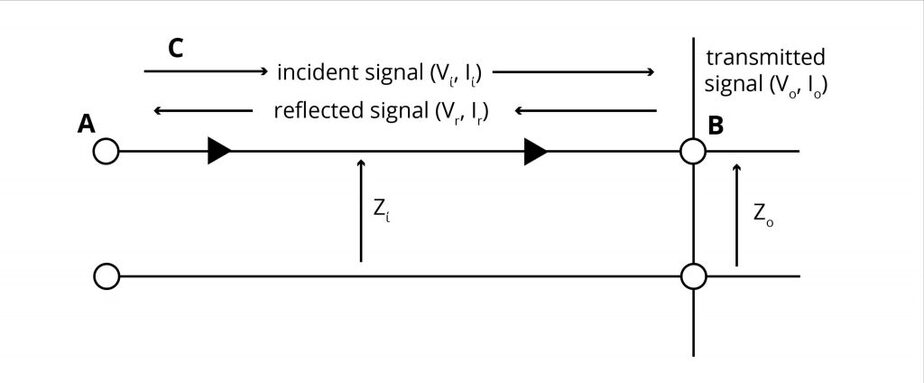

均勻傳輸線上的信號在線路上的所有位置都會遇到恒定阻抗“Zc (V/I)”,并且信號會根據需要沿著它傳輸。但是,如果在任何一點存在阻抗不連續性,信號傳播都會受到影響,并且信號反射會發生,就像光在其傳播的介質中遇到不連續性時會發生反射一樣。

假設從 A 點到 B 點,線路是均勻的,阻抗為“Zi”;但在 B 處,存在阻抗不連續性,并且線路阻抗在 B 處及以后變為“Z0”。

假設信號從 A 在(阻抗為“Zi”的)線上向 B 發送。在 B 處,讓入射信號電壓和電流為“Vi”和“Ii”。那么,我們必須有:

Vi = Zi I0 (1)

現在,如果我們從線路阻抗為“Zo”的右側看 B,那么此時 B 處的傳輸電壓 'Vo' 和傳輸電流 'I0' 必須通過以下方式相關聯:

V0 = Z0 I0 (2)

需要強調的是,關系式(1)和(2)是阻抗概念的基礎,必須始終遵守。

給定“Vi”、“Zi”和“Zo”的值,問題是找到“Vo”的值。

情況 1:Z0 = Zi ,(即線路阻抗沒有不連續性)

在這種情況下,上述方程 (1) 和 (2) 將同時滿足:

V0 = Vi 和 I0 = Ii

這是可以預料的,因為在這種情況下,B 點基本上是均勻傳輸線上的任何點,因此在這條線上的每個 B 點,傳輸的信號將等于入射信號。

情況 2:Z0 ≠ Zi ,(即線路中存在阻抗不連續性)

這里,如果同時看等式(1)和(2),由于Z0≠Zi,很容易得出結論,我們不能同時有Vi=V0和Ii=I0;因為,如果我們暫時假設 Vo = Vi,那么 Ii ≠ I0;如果我們假設 Ii = I0,則 Vo ≠ Vi。因此我們得出的結論是,在阻抗不連續處,入射信號沒有完全完全向前傳輸。

我們能夠滿意地解決這個問題的唯一方法是假設入射信號的一部分在阻抗不連續點 B 反射回來,并且這個反射信號疊加在入射信號上的 B 點和左邊的一條線上其中;在 B 點,入射信號和疊加反射信號的結果將等于 B 點的透射信號。

因此,假設 (Vi,Ii) 的一部分在 B 點反射回“Zi”傳輸線。讓我們用 (Vr,Ir) 表示 B 點反射信號的電壓和電流。

因此,在 B 點,由于入射電壓 Vi 和反射電壓 Vr 產生的信號電壓將為 (Vi + Vr),并且根據在 B 點應用的基爾霍夫定律,這必須等于“Vo”:

V0 = Vi + Vr (3)

由于入射電流“Ii”和反射電流“Ir”(與入射電流方向相反)疊加而產生的電流將為(Ii – Ir),并且根據應用的基爾霍夫定律在 B 點,這必須等于 'Io':

I0 = Ii – Ir (4)

反射 (Vr,Ir) 信號在阻抗為“Zi”的線路上傳播,我們必須有:

Vr = Zi Ir (5)

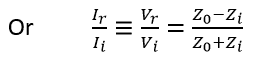

使用等式(3)中的等式(1)、(2)和(5),我們有:

Z0I0 = ZiIi + ZiIr = (Ii + Ir)

因為,根據 (4),I0 = (Ii – Ir),我們有:

Z0 (Ii – Ir) = Zi (Ii + Ir)

或 Ii (Z0 – Zi) = Ir (Z0 + Zi)

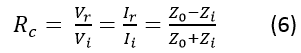

Vr/Vi 或 Ir/Ii 表示在阻抗不連續點 B 反射回來的入射信號的分數,稱為反射系數“Rc”:

就“Rc”而言,B 點傳輸的信號電壓和電流由下式給出:

Vo = Vi + Vr = (1 + Rc) x Vi (7)

并且: Io = Ii – Ir = ( 1 – Rc) x Ii (8)

由上可知,反射系數'Rc'的值取決于'Zi'和'Zo'的相對值;它們之間的差異越大,反射量就越大。可以肯定地得出結論,在阻抗為純電阻的情況下,“Rc”值的范圍可以由下式給出:

-1 ≤ Rc ≤ 1

如果 Z0 > Zi,則部分正信號被反射回來,導致脈沖信號中 B 處的電壓過沖。如果 Z0 < Zi,則部分負信號被反射回來,導致脈沖信號中 B 處的電壓下沖。

我們現在可以討論“Zi”和“Zo”的相對大小的一些特殊情況。

情況 (i):傳輸線以其阻抗終止

這里 Z0 = Zi(因為傳輸線在其遠端 B 端接阻抗值為“Zi”),這導致: Rc = 0 即沒有反射,入射信號將完全傳輸到遠端 B。這個案例告訴我們如何避免傳輸線中的反射:只需在目的地端接一個與傳輸線阻抗相等的阻抗即可。

情況 (ii):傳輸線在遠端開放

這里 Z0 = ∞(因為傳輸線在其遠端 B 處開路),導致 Rc = 1。這意味著入射信號將被完全反射,因此 V0 = 2Vi 和 I0 = 0。這意味著疊加信號電壓將是入射電壓的兩倍,疊加信號電流將為零,正如在開放端所預期的那樣。

情況 (iii):傳輸線短路

此處 Z0 = 0(因為線路在遠端 B 處短路),導致 Rc = -1,因此 V0 = 0 且 I0 = 2Ii。這意味著全入射信號的負值被反射回來,使短路端的電壓如預期的那樣為零。

情況(iv):當Zo≠Zi但差異很小時

如果“Zo”與“Zi”相差約 20%,反射系數“Rc”將為約 10%,這意味著大約 5% 的入射信號將被反射。在大多數電路設計中,由于可用的噪聲容限,阻抗不匹配導致的 10% 信號失真是可以接受的。

各種類型的阻抗不連續性及其可能的原因:

由于傳輸線的阻抗取決于導體的幾何形狀和 PCB 材料特性,因此這些特性的任何變化都會導致阻抗發生變化。此處列出了一些實例:

在線路的源頭或目的地/末端。源阻抗或接收器阻抗通常與線路的阻抗不同。

信號線和返回路徑之間的 PCB 材料的線寬或高度(即銅厚度)的變化或高度和/或介電常數的變化。

信號走線路徑中的過孔:過孔通常沒有與信號走線相同的阻抗——沒有多少設計人員試圖找出過孔是什么阻抗是。優點是過孔長度很小,所以它的效果會以光點的形式出現。過孔的開始將引入一個反射,然后過孔的末端將引入另一個反射。如果過孔阻抗小于線路阻抗,這將導致信號電壓出現小幅下沖。對于非常高速的信號,過孔阻抗不連續性確實很重要,建議設計人員在關鍵信號線中避免它們,如有必要,避免在線中間——而是將它們靠近源和/或目標,以便它們可以與源和目標阻抗不連續一起處理。

如果信號線分支到多個目的地,在分支點,我們會看到阻抗不連續。如果信號線在其路徑上的不同點被抽頭,則在抽頭點處將存在阻抗不連續性。

多次反射:

考慮一條傳輸線,其長度使得其上的總傳播時間為“tp”,并使其阻抗為 50 歐姆。在源端,它連接到一個阻抗為 16.67 歐姆的源,在目的地,它連接到一個 150 歐姆的負載。因此,源處的反射百分比將為 -50%,而在負載時為 +50%。

由源發射的 1V 信號將在時間 0 在線路上降低到 1V x 50/(16.67+50)= 0.75V。在時間“tp”,這個 0.75V 信號將到達目的地,即 50%,即 0。 375V 將被反射回來,使負載電壓 = 1.5×0.75 = 1.125V。現在,0.375V 反射信號將在時間“2tp”到達源,其中 -50% 即 -0.1875V 信號將反射到負載。這將在時間 '3tp' 到達負載,其中 50% = -0.0938V 將被反映,因此將 -0.1875-0.0938 = -0.2813V 添加到 1.125V 的舊負載電壓,使其現在 = 0.8438V。

同時,-0.0938V的反射信號將在時間'4tp'到達源,其中-50% = +0.04688V將被反射到負載;這將在“5tp”到達負載,其中 +50% = +0.02345V 將被反射回來,因此將 +0.04688V +0.02344V = + 0.07032V 添加到負載,使負載電壓現在 = 0.9141V。同時,強度+0.02344V的反射信號將在'6tp'時間到達源,其中-50%即-0.01172V將在'7tp'反射到達負載,其+50%將被反射回來,向負載添加 -0.01172Vx150% = -0.01758V,使負載電壓現在 = 0.9141V-0.01758V= 0.8965V。等等......所以目的地的信號看起來像:

從0到tp:0V

tp到3tp:1.125V

3tp到5tp:0.8438V

5tp到7tp:0.9141V

7tp到9tp:0.8965V

因此,我們將看到目的地的信號振鈴。如果源阻抗小于線路阻抗,導致源端出現負反射,而目的阻抗較高,導致目的端出現正反射,則會出現帶有過沖和下沖的振鈴。

【上一篇:】PCB剛柔結合降低電子產品組裝成本

【下一篇:】如何降低PCB布局中的寄生電容

- 2025-03-20怎么選擇深圳SMT貼片加工廠?

- 2025-02-20深圳SMT貼片加工如何計算報價?

- 2025-06-27軍工級PCBA后焊特殊要求:三防漆涂覆前的清潔度檢測標準

- 2025-06-27自動化替代人工?選擇性波峰焊在插件后焊中的效率與成本對比分析

- 2025-06-26綠色組裝趨勢:無鉛焊接與可降解包裝在PCBA成品組裝中的應用

- 2025-06-26小家電PCBA加工的“高性價比”密碼:如何平衡成本與可靠性?

- 2025-06-26PCBA成品組裝的散熱設計:導熱硅膠、散熱片與風道的協同優化

- 2025-06-25PCBA成品組裝的“零缺陷”挑戰:如何實現99.9%直通率?

- 2025-06-25汽車電子PCBA代工首選:潤澤五洲如何通過IATF 16949認證的12項嚴苛測試?

- 2025-06-24智能硬件PCBA的核心挑戰:如何平衡微型化設計與散熱性能?

- 1怎么選擇深圳SMT貼片加工廠?

- 2深圳SMT貼片加工如何計算報價?

- 3軍工級PCBA后焊特殊要求:三防漆涂覆前的清潔度檢測標準

- 4自動化替代人工?選擇性波峰焊在插件后焊中的效率與成本對比分析

- 5綠色組裝趨勢:無鉛焊接與可降解包裝在PCBA成品組裝中的應用

- 6小家電PCBA加工的“高性價比”密碼:如何平衡成本與可靠性?

- 7PCBA成品組裝的散熱設計:導熱硅膠、散熱片與風道的協同優化

- 8PCBA成品組裝的“零缺陷”挑戰:如何實現99.9%直通率?

- 9汽車電子PCBA代工首選:潤澤五洲如何通過IATF 16949認證的12項嚴苛測試?

- 10智能硬件PCBA的核心挑戰:如何平衡微型化設計與散熱性能?